# Reduction In Harmonic Distortion and Switching Losses Using Multilevel Inverters

Arun Mulimani<sup>1</sup>, Bodigam Ganesh Reddy<sup>2</sup>, Voruganti Bharathkumar<sup>3</sup>, Dr. P. Santosh Kumar Patra<sup>4</sup> <sup>1</sup>Assistant Professor, Department of Electrical and Electronics Engineering, St. Martin's Engineering College, Secunderabad, India <sup>2</sup>Assistant Professor, Department of Electrical and Electronics Engineering, St. Martin's Engineering College, Secunderabad, India <sup>3</sup>Assistant Professor, Department of Electrical and Electronics Engineering, St. Martin's Engineering College, Secunderabad, India <sup>4</sup>Principal and Professor, Department of Computer Science and Engineering, St. Martin's Engineering College, Secunderabad, India

#### Abstract

Use of conventional two-level pulse width modulation (PWM) inverters provide less distorted voltage and current but at the cost of higher switching losses due to high switching frequencies. Multilevel inverters are emerging as a viable alternative for high power, medium voltage applications. This paper compares total harmonic distortion and switching losses in conventional two-level inverters with multilevel inverters (three-level and five-level) at different switching frequencies. An optimized switching frequency has been obtained for a lower level of total harmonic distortion and switching losses. Diode-clamped, three-phase topology is considered for study. A sinusoidal PWM technique is used to control the switches of the inverter. Simulation study confirms the reduction in harmonic distortion and switching losses as the number of the levels increases.

#### Keywords:

Harmonics, Multilevel inverters, Pulse width modulation, Switching losses, Total harmonic distortion.

#### 1. Introduction

Waveforms of practical inverters are non-sinusoidal and contain certain harmonics. For low- and medium-power applications, square wave or quasi-square wave voltage may be acceptable, but for high-power applications, sinusoidal waveforms with low distortion are required. Harmonic contents present in the output of a dc-ac inverter can be eliminated either by using a filter circuit or by employing pulse width modulation (PWM) techniques. Use of filters has the disadvantage of large size and cost, whereas use of PWM techniques reduces the filter requirements to a minimum or to zero depending on the type of application. Traditional twolevel high- frequency PWM inverters have some drawbacks, such as production of common-mode voltages, more switching losses, requirement of switches with very low turn-on and turn-off times, large dv/dt rating, problem of voltage sharing in series connected devices and introduction of large amount of higher order harmonics [1-3].

Multilevel inverters have found better counterparts to the conventional two-level pulse width modulated inverters to overcome the above problems. In addition, they offer the advantage of less switching stress on each device for high voltage, high power applications, with a reduced harmonic content at low switching frequency.

A comparative study of three-level and five-level diode clamped, capacitor clamped and cascaded inverters has

been presented in [4]. The effect of a passive LC filter on the inverter performance was studied. Simulation results indicate reduction in the total harmonic distortion (THD) by using higher number of levels. Switching losses become a dominant part of the total inverter losses at higher switching frequencies. Therefore, optimization of the switching frequency is necessary to reduce both THD and switching losses in the power devices. Switch- ing frequency optimization was not considered in [4]. Switching losses and THD in threelevel and five-level diode clamped inverters can also be optimized by using space vector PWM technique [5-7].

This paper investigates two-level inverters and threelevel and five-level diode clamped three-phase inverters on the basis of the THDs and switching losses at different switching frequencies. An extensive simulation study to optimize the switching frequency based on the corresponding switching losses and THD contents in line voltage have been presented in this paper. A sinusoidal pulse width modulation (SPWM) technique is used for control.

Section 2 of the paper gives a system description of two-level, three-level and five-level inverters, whereas Section 3 presents the methodology for the switching loss calculation. Section 4 discusses the modulation tech- niques for two-level, three-level and five-level inverters and the last section compares these topologies on the basis of switching losses and THD at different switching frequencies. Switching frequency optimization has been carried out to achieve a low level of both THD and switching loss.

#### 2. Basics of Two-Level And Multilevel Inverters

#### **Two-Level Inverters**

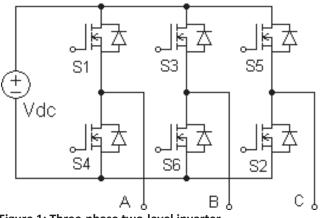

This is the most widely used topology in various lowand medium-power applications. The full-bridge configuration of the three-phase voltage source inverter is shown in Figure 1. The switching logic to obtain output voltage for a 120<sub>0</sub> mode of operation is shown in Table 1. This topology can be used at a very high switching frequency to obtain low THD by using PWM techniques. Power devices are to be connected in series–parallel to achieve a large power capability. They suffer from static and dynamic voltage sharing problems in series and parallel connection of power devices, high rate of change of voltage due to synchronous commutation of series devices and inclusion of high switching frequency harmonic contents in inverter output voltage [3].

#### **Multilevel Inverters**

Multilevel inverters have grown as better counterparts to conventional two-level inverters. Commonly employed multilevel inverter topologies are Diode Clamped, Capacitor Clamped and Cascaded Multilevel inverters. In all these topologies, the output voltage is synthesized from several levels of input voltages obtained from several capacitors connected across the dc bus. In a capacitor clamped inverter, both real and reactive power can be controlled, but it suffers from higher switching losses due to real power transfer thus reducing the efficiency of power conversion. Also, it requires a large number of storage capacitors at higher levels. The cascaded inverter uses a large number of separate dc sources for each of the bridges. However, in the diode clamped topology, all devices are switched at the fundamental frequency resulting in low switching losses and high efficiency. Other main features of this topology are controlled reac- tive power flow between source and load, much better dynamic voltage sharing among switching devices and

Table 1: Switching states of a two-level three-phase inverter

| Load line vo                               | ltage | ge Switching states |    |                |    |                |  |

|--------------------------------------------|-------|---------------------|----|----------------|----|----------------|--|

| (V <sub>AB</sub> )                         | S1    | S₂                  | S₃ | S <sub>4</sub> | S₅ | S <sub>6</sub> |  |

| +\/. /2                                    | 1     | 0                   | 0  | 0              | 0  | 1              |  |

| +V <sub>dc</sub> /2<br>+V <sub>dc</sub> /2 | 1     | 1                   | 0  | 0              | 0  | Ō              |  |

| 0                                          | 0     | 1                   | 1  | 0              | 0  | 0              |  |

| -V <sub>dc</sub> /2<br>-V <sub>dc</sub> /2 | 0     | 0                   | 1  | 1              | 0  | 0              |  |

| -V <sub>dc</sub> /2                        | 0     | 0                   | 0  | 1              | 1  | 0              |  |

simple topological structure. Therefore, diode clamped inverter topology is considered here for study. The control logic is simple, especially for back-to-back inter-tie connections of two systems. However, it requires a large number of clamping diodes for a large number of output voltage levels. To produce an m-level output phase voltage, (m-1) switches are required for each half phase leg, a total of (m-1) dc link capacitors for energy storage and (m-1)\*(m-2) clamping diodes for each phase leg [1-2].

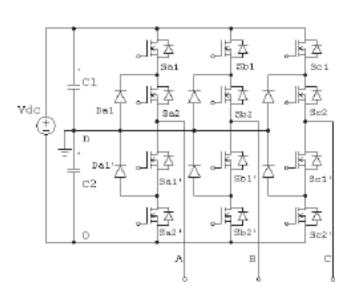

#### Three-Level Diode Clamped Multilevel Inverter (DC-MLI)

Three-phase diode clamped three-level inverter (neutral point clamped) topology is shown in Figure 2. The circuit consists of two dc link capacitors, 12 power switches and six clamping diodes. The middle point of the dc bus capacitor is known as neutral point 'n'. The main feature of this topology is clamping diodes that clamp the switch voltage to half of the dc bus voltage, reducing the voltage stress of the switching device. The output voltage has three different states: +, 0 and – and the corresponding

output phase voltages are  $+V_{dc}/2$ , 0 and  $-V_{dc}/2$ . Switching states to synthesize the output voltages for phase 'A' are defined in Table 2. A similar logic can be applied for the other two phases.

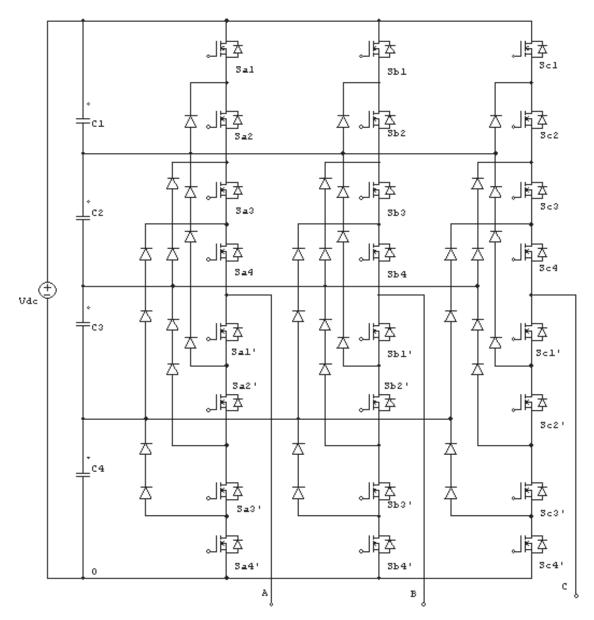

#### Five-Level DCMLI

The circuit diagram of the five-level DCMLI topology is shown in Figure 3. It consists of 24 power switches and 36 clamping diodes. The DC bus has four capacitors for a DC bus voltage  $V_{dc}$ . The voltage across each capacitor

Figure 1: Three-phase two-level inverter.

Table 2: Switching states for phase 'A' of a three-level diode clamped inverter

| S  | S  | <b>S'</b> <sub>a1</sub> | <b>S'</b> a2 | Switching Output pole Output |                           |                     |  |

|----|----|-------------------------|--------------|------------------------------|---------------------------|---------------------|--|

| a1 | a2 |                         |              | phase                        | voltage                   |                     |  |

| a1 | 42 |                         |              | (V)                          | voltage <sub>A</sub> (V ) | An                  |  |

| 1  | 1  | 0                       | 0            | +                            | + V <sub>dc</sub>         | +V <sub>dc</sub> /2 |  |

| 0  | 1  | 1                       | 0            | 0                            | +V <sub>dc</sub> /2       | 0                   |  |

| ^  | ^  | -1                      | -            |                              | 0                         | · · · -             |  |

is  $V_{\rm dc}/4;$  thus, the voltage stress across each device will be limited to  $V_{\rm dc}/4$  through the clamping diode. Table 3 shows the switching combinations and correspond- ing output phase voltage levels where switching state '1' represents the switch is in 'on' condition and state

'0' indicates the switch is in 'off' condition. When the number of levels is high enough in the DCMLI, harmonic contents in the output voltage and current get reduced to avoid the need for filters.

#### 3. Switching Loss Calculations

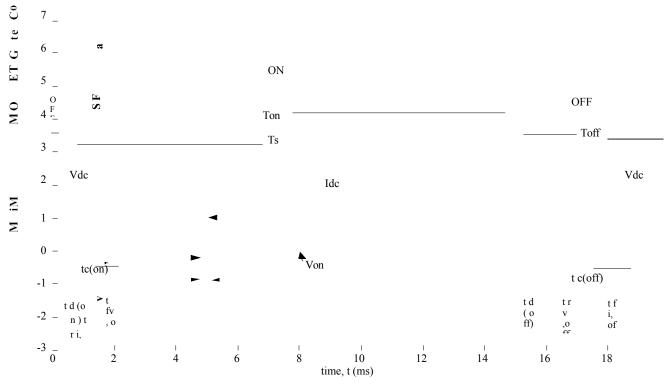

Consider a single MOSFET switch connected across a dc voltage of value V<sub>dc</sub>. Current through switch during 'on' time is considered as  $I_{dc}$ . Figure 4 shows the waveforms

#### ISSN NO:2231-3990

Instantaneous power during the interval  $t_{c(on)}$  is p(t) $= v(t)^{*}i(t)$

dc

$$= \{ V_{dc} - (V_{dc} - V_{on})^{*} (t/t_{c(on)}) \}^{*} \{ I_{dc}^{*} (t/t_{c(on)}) \} \\= \{ V^{*}I^{*} (t/t_{1})^{*} \} - (V^{-}V^{-})^{*} (t_{2}^{2}/t_{2})$$

(3)

dc dc c(on) on c(on) and energy dissipated during this interval is  $t_{c(m)}$

$$E_{c, on} = \int [\{V_{dc} * I_{dc} * (t/t_{c(on)})\} - (V_{dc} - V_{on}) * (t_2/t_2)] dt 0 to$$

$$t_{c(on)} = (V * I * t_2)/2 - (V - V) * I_{c(on)}$$

$$E_{c, on \ dc \ dc} = (V_{dc} * I_{dc} * t_{c(on)})/6 - (V_{on} * I_{dc} * t_{c(on)})/3 \qquad (4)$$

and during turn-off transition, of t  $_{c(off)}$ , the current

of the voltage across and the current through the switch when it is operated at a switching frequency of F = 1/T,

## falls from $L_{\rm c}$ to zero and the $V_{\rm c}$ rises linearly to $V_{\rm c}$ . The instantaneous voltage and current ouring this pe-

where  $T_{\rm s}$  is the switching period. To simplify the expressions, the switching waveforms are represented by linear

v(t) = V + (V - V)/t

### ISSN NO:2231-3990

(5)

approximations In the figure,  $v_M$  and  $i_M$  are the voltage

| on                 | C  | on | c(off) | (6) |

|--------------------|----|----|--------|-----|

| <sup>dc</sup> I /t |    |    |        |     |

|                    | dc | dc | c(off) |     |

across and the current through the MOSFET [3, 5].

| Switching losses can be calculated from the turn-on     | and t |

|---------------------------------------------------------|-------|

| characteristics of the devices. Instantaneous volt- age | and o |

| during turn on time t <sub>c(m)</sub> are               |       |

Figure 2: Three-phase three-level diode clamped inverter.

Hence, the energy dissipated can be

$\begin{aligned} &\text{found as } t_{c(off)}, \ E_{c, off} = \int [V_{on} * I_{dc} + (V_{dc} - V_{on}) * I_{dc} * (t/t_{c(off)}) - V_{on} * I_{dc} \\ & * (t/t_{c(off)}) - (V_{dc} - V_{on}) * I_{dc} * (t_2/t_2)] \ dt \qquad 0 \\ &t_{c(on)} \\ &= (V_{dc} * I_{dc} * t_{c(off)})/6 - (V_{on} * I_{dc} * t_{c(off)})/3 \end{aligned}$

With a switching frequency of  $F_s$ , the average switching loss in the switch during each transition of turn on and turn off can be found as

$$\begin{split} P_{c, on} &= (V_{dc} * I_{dc} * t_{c(on)} / T_s) / 6 + (V_{on} * I_{dc} * t_{c(on)} / T_s) / 3 \quad (9) \\ P_{c, off} &= (V_{dc} * I_{dc} * t_{c(off)} / T_s) / 6 - (V_{on} * I_{dc} * t_{c(off)} / T_s) / 3 \quad (10) \end{split}$$

Hence, the average switching loss  $P_{sw}$  in the switch is  $P_{sw}$  = (1/6)\*V\_{dc}\*I\_{dc}\*\{t\_{c(on)} + t\_{c(off)}\}/T\_s + (1/3)\*V\_{on}\*I\_{dc}\*\{t\_{c(on)} + t\_{c(off)}\}/T\_s

(11)

#### Table 3: Switching states for phase 'A' of a five-level diode clamped inverter

| Sal | S <sub>a2</sub> | S <sub>a3</sub> | S <sub>a4</sub> | <b>S'</b> a1 | <b>S'</b> a2 | <b>S'</b> <sub>a3</sub> | <b>S'</b> <sub>a4</sub> | Output phase voltage | Output pole voltage |

|-----|-----------------|-----------------|-----------------|--------------|--------------|-------------------------|-------------------------|----------------------|---------------------|

|     |                 |                 |                 |              |              |                         |                         | (V <sub>An</sub> )   | (V <sub>Ao</sub> )  |

| 1   | 1               | 1               | 1               | 0            | 0            | 0                       | 0                       | +V <sub>dc</sub> /2  | V <sub>dc</sub>     |

| 0   | 1               | 1               | 1               | 1            | 0            | 0                       | 0                       | +V <sub>dc</sub> /4  | 3V <sub>dc</sub> /4 |

| 0   | 0               | 1               | 1               | 1            | 1            | 0                       | 0                       | 0                    | $V_{dc}/2$          |

| 0   | 0               | 0               | 1               | 1            | 1            | 1                       | 0                       | -V <sub>dc</sub> /4  | V <sub>dc</sub> /4  |

| 0   | 0               | 0               | 0               | 1            | 1            | 1                       | 1                       | -V <sub>dc</sub> /2  | 0                   |

(8)

c(off)

c(off)

Eqn. (11) shows that the switching power loss in a semi- conductor switch varies linearly with the switching fre- quency and switching times. Therefore, with the devices having short switching times, it is possible to operate

them at a higher switching frequency thus avoiding excessive switching power losses in the device [8-10]. Nomenclature of variables used are given in Appendix-I

Figure 3: Three-phase five-level diode clamped inverter.

#### **Appendix I: Nomenclature**

| v(t), i(t), p(t)     | instantaneous voltage, current and power              | Pc, on, Pc, off      | average switching loss during t $_{c(on)}$ and t $_{c(off)}$ |

|----------------------|-------------------------------------------------------|----------------------|--------------------------------------------------------------|

| V <sub>dc</sub>      | voltage across switch when turned-off                 | Ts                   | sampling time in sec                                         |

| Von                  | voltage across switch when turned-on                  | Fs                   | switching frequency in Hz                                    |

| t                    | time in sec                                           | Psw                  | average switching loss in watts                              |

| t <sub>c(on)</sub>   | turn-on cross-over interval                           | t <sub>d(on)</sub>   | turn-on delay time                                           |

| $\mathbf{I}_{dc}$    | current through switch when turned-on                 | t <sub>ri, on</sub>  | turn-on current rise time                                    |

| E c, on              | energy dissipated during turn-on cross-over interval  | t <sub>fv. on</sub>  | turn-on voltage fall time                                    |

| _t <sub>c(off)</sub> | turn-off cross-over interval                          | t <sub>d(off)</sub>  | turn-off delay time                                          |

| E c, off             | energy dissipated during turn-off cross-over interval | t <sub>rv, off</sub> | turn-off voltage rise time                                   |

|                      |                                                       | t fi off             | turn-off current fall time                                   |

### Volume IX, Issue IV, April/2020

### Page No:2561

Figure 4: Linearized switching characteristics.

whereas load parameters considered for simulation study are given in Appendix-II.

#### 4. Modulation Technique

Modulation techniques for voltage source inverters may be carrier based or carrier-less and open loop or closed loop. These modulation or control techniques for multilevel voltage source inverters are classified in Figure 5. Simulation investigation of different multilevel control techniques have been presented in [11]. The SPWM technique is considered for study in this paper. It is the simple technique to be implemented. In the SPWM technique, a triangular carrier wave at a high switching frequency is compared with the sinusoidal reference wave at a fundamental output frequency. The SPWM technique is again divided into Alternate Phase Opposition Disposition, Phase Opposition Disposition and In Phase (PH) [12].

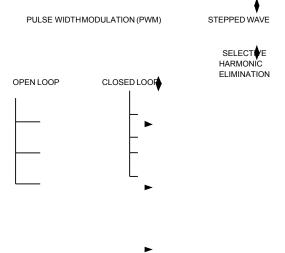

Figure 6 shows the generation of switching pulses for power device  $S_1$  of the two-level inverter shown in Figure 1. One triangular carrier wave is compared with a sinusoidal reference wave to generate switching pulses. For power device  $S_4$ , the complementary of this pulse is to be given. The control principle of the SPWM is to use several triangular carrier signals keeping only one modulating sinusoidal signal. If an m-level inverter is

#### **Appendix II: Simulation parameters**

| Load parameters         | MOSFE                | MOSFET parameters |  |  |

|-------------------------|----------------------|-------------------|--|--|

| Three-phase             | t <sub>c(on)</sub>   | 48 ns             |  |  |

| active power 8          | t <sub>d(on)</sub>   | 15 ns             |  |  |

| kW                      |                      |                   |  |  |

| Three-phase inductive   | t <sub>ri, on</sub>  | 25 ns             |  |  |

| reactive power 6 kVar   | t <sub>c(off)</sub>  | 85 ns             |  |  |

| Nominal frequency 50 Hz | t d(off)             | 52 ns             |  |  |

| Nominal phase-phase     | t <sub>fi, off</sub> | 25 ns             |  |  |

| voltage                 | •                    | 200 Volts         |  |  |

ns: nanoseconds

employed, (m-1) level shifted carriers will be needed.

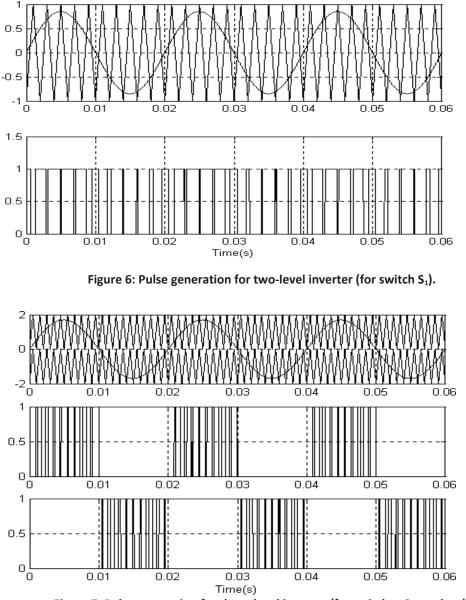

Two and four triangular carrier signals are needed for three- and five-level inverters, respectively. The carriers have the same frequency f<sub>c</sub> and the same peak-topeak amplitude Ac. The zero reference is placed in the middle of the carrier set. The modulating signal is a sinusoid of frequency f<sub>m</sub> and amplitude A<sub>m</sub>. At every instant, each carrier is compared with the modulating signal. Each comparison switches the switch 'on' if the modulating signal is greater than the triangular carrier assigned to that switch. Obviously, the actual driving signals for the power devices can be derived from the results of the modulating-carrier comparison by means of a control logic circuit. Figure 7 shows the generation of switching pulses for power devices  $S_{a1}$  and  $S_{a2}$  of the three-level inverter shown in Figure 2. Pulses for the lower two devices S and S are complementary to these pulses,

a1 a2

### ISSN NO:2231-3990

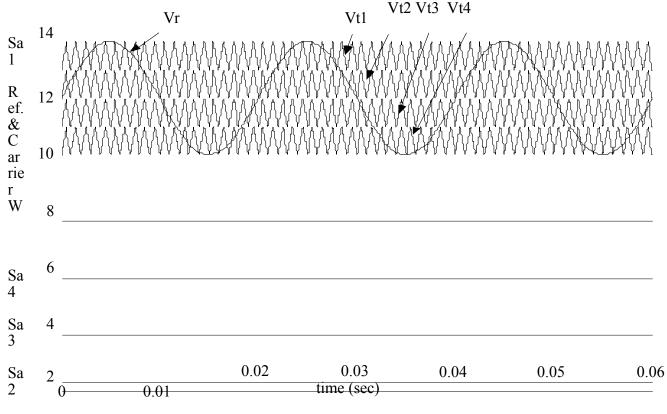

respectively. Figure 8 shows the generation of switching

pulses for power devices <sub>a1, a2</sub>, of the fiveand S S S<sub>a3</sub>  $S_{a4}$ level Inverter shown in Figure 3. Pulses for the lower are complementary to four devices S , S , S and S a2 a1 a3

these pulses, respectively.  $V_r$  is the reference sin wave and  $V_{t1}$ ,  $V_{t2}$ ,  $V_{t3}$ ,  $V_{t4}$  are four carrier signals.

a4

#### \$. Simulation Study of DCMLI With SPWM

SINUSOIDAL

SPACE VECTOR

SIGMA DELTA

Volume IX, Issue IV, April/2020

### ISSN NO:2231-3990

### Alochana Chakra Journal

| HYSTERISIS        | After modeling the                     |

|-------------------|----------------------------------------|

| CURRENT           | control logic of the                   |

| CONTROLLER LINEAR | SPWM technique<br>as discussed in      |

| CURRENT           | section 4,                             |

| CONTROLLER        | simulation studies                     |

| DIGITAL DEAD BEAT | have been<br>performed on two-         |

| CURRENT           | level, three-level                     |

| CONTROLLER        | and five-level diode                   |

| OPTIMIZED CURRENT | clamped three-<br>phase inverters. The |

| CONTROLLER        | output voltage wave-                   |

Figure 5: Classification of multilevel control techniques [12].

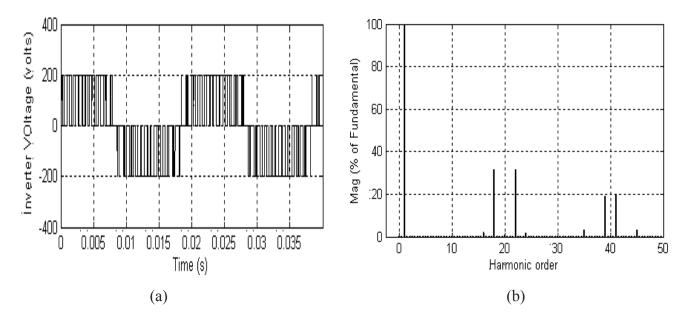

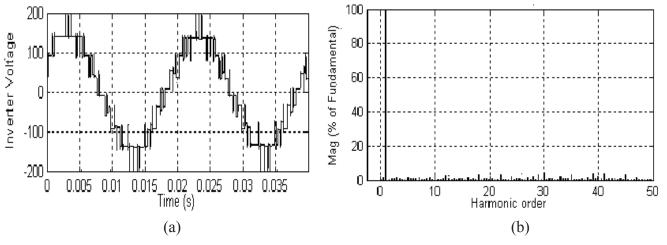

form and its frequency spectrum for a two-level inverter at a switching frequency of 1 kHz are shown in Figure

Figure 7: Pulse generation for three-level inverter (for switches Sa1 and sa2).

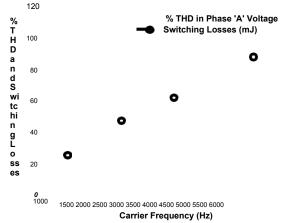

9. Table 4 gives the THD and switching losses in each phase voltage at different switching frequencies. As the switching frequency is increased THD is reduced. The total switching losses are calculated as discussed in sec- tion 3, and tabulated in Table 5 for the different carrier frequencies ranging from 1500 to 5000 Hz.

It can be observed from Table 4 that a decrease in the car- rier frequency results in a lower value of switching losses. This is due to the reduced number of 'sampling points' at reduced carrier frequencies, which in turn limit the

number of switching transitions in one PWM switching

cycle, resulting in lower switching losses. Lowering the value of the carrier frequency still preserves the average shape of the fundamental 50 Hz sinusoidal but exhibits an increase in the THD due to increased 'notches' within the width of each generated output pulse. To locate the optimum point whereby both THD and switching losses are optimized, the performance of the two-level converter is observed at several carrier frequencies and the values of THD and switching losses are noted.

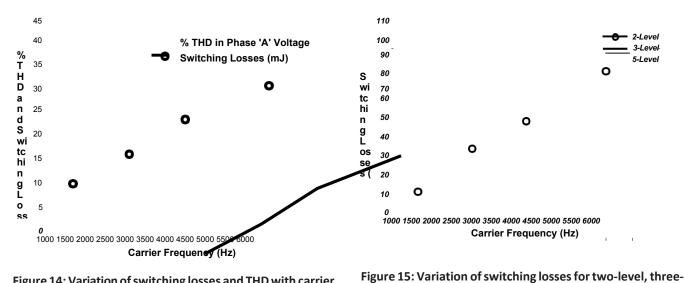

From the values of THD and switching losses obtained, a graph of THD and switching losses with reference to carrier frequencies is constructed to locate the optimum point with minimized losses, as shown in Figure 10. From Figure 10 it is clear that at the switching frequency of 2300 Hz, THD and switching losses are optimized. Table 4: THD and switching losses for a two-level inverter at different switching frequencies

| Carrier   |           | % THD        | To      | tal     |

|-----------|-----------|--------------|---------|---------|

| switching |           | (Hz) Phase A | Phase B | Phase C |

|           | losses (n | nJ)          |         |         |

| 1500      | 44.26     | 44.35        | 44.82   | 25.80   |

| 2500      | 40.48     | 40.73        | 40.63   | 47.68   |

| 3500      | 37.56     | 37.42        | 37.61   | 62.35   |

| 5000      | 31.83     | 31.54        | 31.67   | 88.18   |

|           |           |              |         |         |

THD: Total harmonic distortion

Table 5: THD and switching losses for a three-level inverter at different switching frequencies

| Carrier  |                          | % THD               | Tot     | al      |

|----------|--------------------------|---------------------|---------|---------|

| switchin | g frequency<br>losses (n | (Hz) Phase A<br>nJ) | Phase B | Phase C |

| 1500     | 34.10                    | 34.13               | 33.94   | 21.88   |

| 2500     | 22.05                    | 22.39               | 22.52   | 31.86   |

| 3500     | 14.68                    | 14.93               | 14.89   | 39.40   |

| 5000     | 8.97                     | 8.64                | 9.16    | 46.64   |

THD: Total harmonic distortion

| Table 6: THD and switching losses for the five- | level |

|-------------------------------------------------|-------|

| inverter at different switching frequencies     |       |

| Carrier           |                      | Total |       |                             |  |

|-------------------|----------------------|-------|-------|-----------------------------|--|

| frequency<br>(Hz) | Phase A Phase B<br>C |       | Phase | switching<br>losses<br>(mJ) |  |

| 1500              | 25.94                | 25.66 | 24.93 | 13.42                       |  |

| 2500              | 19.18                | 19.64 | 20.21 | 19.47                       |  |

| 3500              | 8.18                 | 8.83  | 8.44  | 26.60                       |  |

| 5000              | 6.31                 | 5.37  | 5.84  | 33.33                       |  |

THD: Total harmonic distortion

Figure 8: Pulse generation for five-level inverter (for switches Sa1, sa2, sa3 and sa4).

Figure 9: output voltage of two-level inverter and its frequency spectrum.

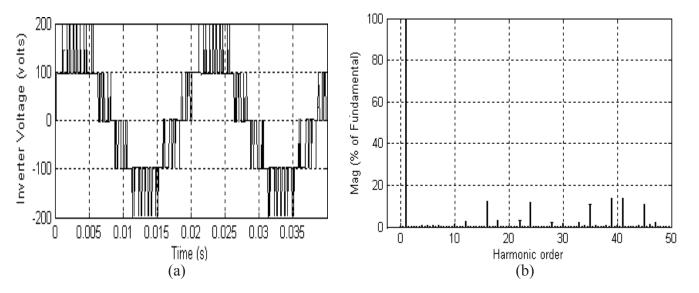

Output voltage waveform and its frequency spectrum for the three-level inverter at a switching frequency of 1 kHz are shown in Figure 11. The THD and the total switching losses are calculated and tabulated in Table 5 for different carrier frequencies ranging from 1500 to 5000 Hz. From the simulation results and analysis taken for the three-level three-phase inverter, it is observed that with the increase in the number of levels, the system per- formance is improved in terms of the THD and switching losses. The voltage impressed across the terminals of the switches is reduced from 200 to 100 volts as compared to the two-level inverter. However, it is also observed that an unequal device rating would be necessary for the three-level inverter.

To obtain the output voltage corresponding to that of  $V_{dc}$  of the input voltage, both switches  $S_{a1}$  and  $S_{a2}$  have to be turned on. However, to produce the level of  $0.5V_{dc}$ , switch  $S_{a2}$  remains on while  $S_{a1}$  turns off. It shows that switch  $S_{a2}$  remains on for one switching sequence more than that of  $S_{a1}$  and  $S_{a2}$  conducts over the entire cycle except when the output voltage is equal to zero. Such unequal conduction duty requires different ratings for the switching devices. When the inverter is designed to use the average duty for all devices, the outer switches may be oversized and the inner switches may be under-sized. Because of this reason, it is observed that switching losses were considerably reduced as compared with that of the two-level inverter.

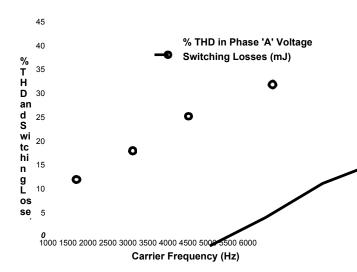

According to Table 5, switching losses were reduced to almost half with a decrease in the switching frequency from 5000 to 1500 Hz. However, this is achieved at an

Figure 10: Variation of switching losses and THD with carrier frequency for the two-level inverter.

expense of an increase in the THD level. For different carrier frequencies, the switching loss and THD levels associated with different carrier frequencies were observed and a graph of variation of THD and switching loss with carrier frequency is constructed to locate the optimum point, as shown in Figure 12.

The output voltage and its frequency spectrum of a five-level inverter at a switching frequency of 1 kHz are shown in Figure 13. The system performance for the five-level inverter is further improved in terms of the THD and switching losses. The voltage impressed across the terminals of the switches is further reduced to 50 volts from 200 volts as in the two-level inverter. However, it is also observed that unequal device rating would be

### Volume IX, Issue IV, April/2020

Figure 11: output voltage of the three-level inverter and its frequency spectrum.

# Figure 12: Variation of switching losses and THD with carrier frequency for the three-level inverter.

necessary for the five-level inverter as well, similar to that of the three-level topology. From Table 3, it can be seen that to obtain an output voltage corresponding to that of V<sub>dc</sub> of the input voltage, all top switches have to be turned on. However, to produce the level of  $0.75V_{dc}$ , switches S<sub>a2</sub>, S<sub>a3</sub> and S<sub>a4</sub> remain on while S<sub>a1</sub> turns off and its complement Sa1' turns on. This continues until a volt- age output of  $0.5V_{dc}$  is required, which in turn causes Sa2 to turn off and its complement Sa2 to be turned on. When a voltage level of  $0.25V_{dc}$  is needed, S<sub>a3</sub> turns off while S<sub>a4</sub> remains on. Hence, it can be seen that  $a_{a_4}$  remains on for three switching sequences allowing it to conduct over the entire cycle except when the output voltage required is zero. Such unequal conduction duty cycle requires the switches to be sized differently in terms of both their

Volume IX, Issue IV, April

current and their voltage ratings. When the inverter design is to use the average duty for all devices, the outer switches may be oversized and the inner switches may be undersized as in the three-level inverter.

Table 6 shows the total switching losses and % THD in each phase voltage for different carrier frequencies ranging from 1500 to 5000 Hz for a five-level inverter. It is noted that switching losses are considerably reduced than that of the two-level and three-level inverters main- ly due to the fact that the voltage across the terminals of the switch is considerably lesser.

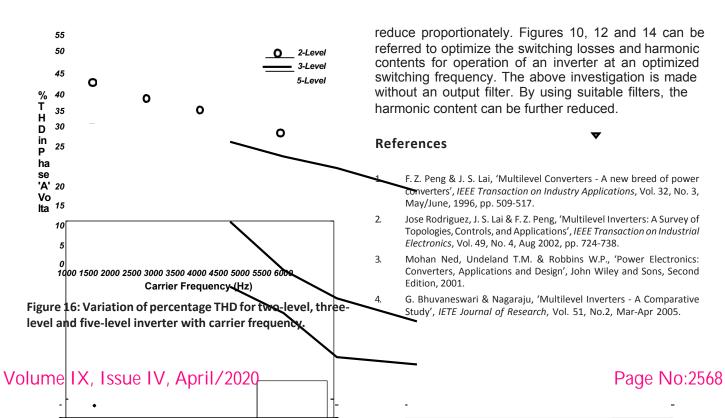

Variation of THD and switching losses for different carrier frequencies is constructed to locate the optimum point, as shown in Figure 14. Figures 15 and 16 show the variation of switching losses and THD for two-level, three-level and five-level inverters, respectively. It is observed that switching losses reduce with increased number of levels in output voltage at a particular switching frequency. However, for the same inverter level, switching losses increase with switching frequency. It is clear from Figure 16 that THD reduces with number of inverter levels and also with switching frequency.

#### 6. Conclusion

A comparative study of THD of the output voltage waveform and switching losses of two-level, three-level and five-level three-phase diode clamped inverters has been presented in this paper using the SPWM technique. It has been observed that both THD and switching losses decrease with the increase in the number of levels in the output voltage. However, with the decrease in carrier frequency, the THD level increases and switching losses

Figure 13: output voltage of a five-level inverter and its frequency spectrum.

level and five-level inverters with carrier frequency.

Figure 14: Variation of switching losses and THD with carrier frequency for a five-level inverter.

- B. Kaku, I. Miyashita & S. Sone, 'Switching Loss Minimized Space Vector PWM Method for IGBT Three-Level Inverter', *IEE Proceedings, Electric Power Applications*, Vol. 144, No. 3, May 1997, pp 182-190.

- Markku Jokinen & Anssi Lipsanen, 'Fundamental Study of 2-Level and 3-Level frequency Converters', Assignment on converter Losses, SMOLA, Norway, 2005.

- Trzynadlowski A. M., 'Space Vector PWM Technique with Minimum Switching Losses and a Variable Pulse Rate', *Conference Proceedings* of *IECON* 1993, pp. 689-694.

- Richard Lund, Jonas B., Sigurd O. & Roy Nilsen, 'Analytical Power Loss Expressions for diode Clamped Converters', *EPE-PEMC*, Dubrovnik and Cavtat, 2002.

- A.D. Rajapakse, A.M. Gole & P.L. Wilson, 'Approximate Loss Formulae for Estimation of IGBT Switching Losses through EMTP-type Simulations', *IPST-2005*, Montreal, Canada, Jun 19-23, 2005, Paper no, IPST05-184.

- 10. Alain Laprade & Ron H. Randall, 'Numerical Method for Evaluating IGBT Losses', *Application Notes, Fairchild Semiconductors*, Jan 2000, AN-7520.

- P. K. Chaturvedi, Shailendra K. Jain, Pramod Agrawal & P. K. Modi, 'Investigations on Different Multilevel Inverter Control Techniques by Simulation', *PEDES-2006*, New Delhi, 12-15 Dec 2006, CD Rom, Paper No 3C-12.

- Massoud A.M., Finney S.J. & Williams B.W., 'Control techniques for multilevel voltage source inverters', 34<sub>th</sub> Power Electronics Specialist Conference, Jun 15-19, 2003, Vol - I, pp. 171-176.

### ISSN NO:2231-3990